DP/eDP

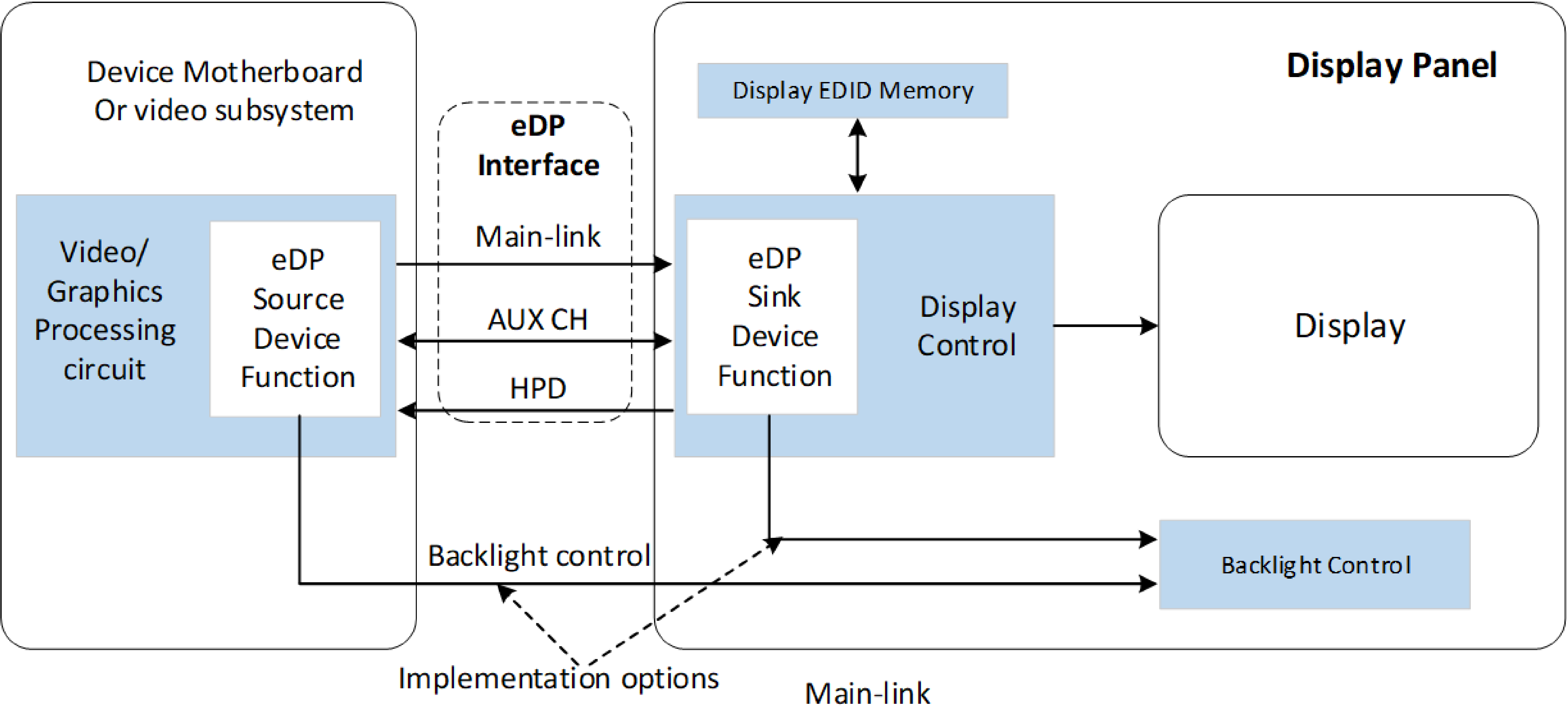

Innosilicon DP/eDP IP is designed for transmitting or receiving

video and audio signals between the video source devices and

display devices. It is fully compliant with DP1.4 and eDP1.4

specifications. The IP provides both PHY and controller solutions,

offering a reliable implementation for DisplayPort and embedded

DisplayPort interfaces that can be seamlessly integrated in the

SoCs used in multimedia devices.